芯(xīn)片描(miáo)述

芯(xīn)片特點

| ○ | 2k×16-bit otp rom | ○ | 80×8-bit sram | |

| ○ | 8 級(jí)堆棧(zhàn)空(kōng)間(jiān) | ○ | 可編(biān)程 wdt 預(yù)分(fèn)頻器 | |

| ○ | 可(kě)編程(chéng) wdt 時間(4.5ms、18ms),可控制 wdt 自由運行時(shí)間 | ○ | 帶信号源(yuán)選擇、觸發沿選擇(zé)、溢出中斷(duàn)及預分頻(pín)器(qì)的 8 位實時時(shí)鍾/計數(tcc) | |

| ○ | 工(gōng)作電壓範(fàn)圍:2.1v~5.5v(-0℃~70℃)2.3v~5.5v(-40℃~85℃) | ○ |

工(gōng)作頻率範圍(2 分(fèn)頻):

晶振模(mó)式:dc~16mhz,4.5v;dc~8mhz,3v; dc~4mhz,2.1v erc 模式:dc~2mhz,2.1v irc 模(mó)式:16mhz,4mhz,1mhz,8mhz |

|

| ○ | 系(xì)統高(gāo)低(dī)頻率的界限是 400khz | ○ |

低功耗(hào):

小于(yú) 1.5ma(4mhz/5v) 典型 15a (32khz/3v) 典(diǎn)型(xíng) 2a(睡眠(mián)模式(shì),wdt 關(guān)閉(bì),lvd 關閉(bì)) |

|

| ○ | 内置(zhì) rc 振蕩(dàng)電路(lù):16mhz、1mhz、4mhz、8mhz | ○ | 低(dī)壓複位:4.0v±0.3v、3.5v±0.3v、2.7v±0.3v @25℃ | |

| ○ | 低壓(yā)檢測:4.5±0.2v、4.0±0.2v、3.3±0.2v、2.2±0.2v @25℃ | ○ |

中(zhōng)斷源:

tcc 溢出中斷 (idle 模式喚(huàn)醒) 外部(bù)中(zhōng)斷 (sleep/idle 模(mó)式喚醒(xǐng)) 比較器(qì)輸出狀(zhuàng)态(tài)改變中斷 (sleep/idle 模式喚醒(xǐng)) adc 轉換完成中斷 (sleep /idle 模式喚(huàn)醒) pwm1~3 周期(qī)中斷(duàn) (idle 模式(shì)喚醒(xǐng)) pwm1~3 占空比(bǐ)中斷 (idle 模(mó)式喚醒) p0 端(duān)口輸(shū)入狀态改變中(zhōng)斷 (sleep /idle 模式(shì)喚醒) lvd 中(zhōng)斷 (sleep /idle 模式喚醒) |

|

| ○ |

雙(shuāng)向 i/o 口:

17 位可編程(chéng)控制 pull-high i/os(p1<7:0>,p0<7:0>,p20) 16 位可編程(chéng)控制(zhì) open-drain i/os(p1<7:0>,p0<7:0>) 17 位可編程控制(zhì) pull-low i/os(p1<7:0>,p0<7:0>,p20) 14 位可編程(chéng)控制(zhì) high-sink current i/os (p1<7:0>,p0<7:6>,p0<4:1>) |

○ | 指(zhǐ)令(lìng)周期(qī)長度(dù)選擇:2/4/8/16 個振(zhèn)蕩時鍾 | |

| ○ | 封裝形式:dip/sop/ssop20,dip/sop18 |

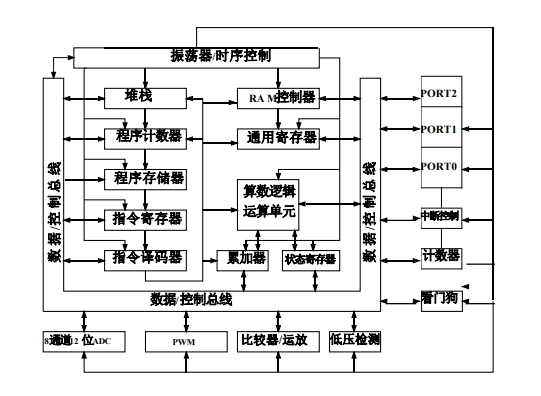

芯(xīn)片框圖

産品中(zhōng)心

關(guān)于我們

無(wú)錫總部

0510-85381221

地(dì)址:無錫市濱湖(hú)區建(jiàn)築西路599号(hào)3号樓(lóu)9樓

郵(yóu)箱:hrm@gxds.cc

無錫分(fèn)公司(sī)

地址:無錫市清(qīng)源路(lù)20号立(lì)業樓e201-3

深圳(zhèn)分公司

0755-82916151

地(dì)址(zhǐ):深(shēn)圳市福田區蓮(lián)花街(jiē)道北(běi)環大道7057号武警大廈(shà)(辦公樓)1002室(shì)

傳真(zhēn):0755-83466827